| TEST di autovalutazione |

| 1 | Lo stato SET del LATCH SR che rappresenta il simbolo 1 corrisponde alla configurazione in cui: | ||

| A) | Gli output sono entrambi uguali a 1 | ||

| B) | Gli output sono diversi e l'output Q=0 | ||

| C) | Gli output sono diversi e l'output Q=1 | ||

| D) | Gli output sono entrambi uguali a 0 | ||

| 2 | Lo stato RESET del LATCH SR che rappresenta il simbolo 0 corrisponde alla configurazione in cui: | ||

| A) | Gli output sono diversi e l'output Q=1 | ||

| B) | Gli output sono entrambi uguali a 1 | ||

| C) | Gli output sono entrambi uguali a 0 | ||

| D) | Gli output sono diversi e l'output Q=0 | ||

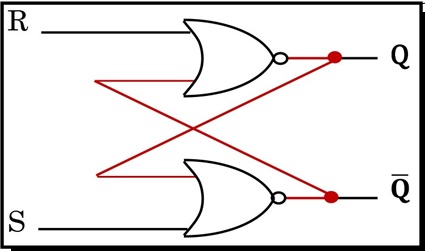

| 3 |

A partire dal LATCH SR riportato in figura, il circuito del Flip/Flop SR si ottiene: |

||

| A) | Ponendo R = NOT(S) | ||

| B) | Ponendo S = NOT(R) | ||

| C) | Introducendo il segnale clock posto in AND con ciascuno degli input S ed R | ||

| D) | Eliminando la temporizzazione | ||

| 4 | Nel Flip-Flop SR l'input S=0 ed R=0 determina: | ||

| A) | La transizione dei valori output nello stato SET | ||

| B) | Il mantenimento invariato dello stato rappresentato dai valori output | ||

| C) | La transizione dei valori output nello stato RESET | ||

| D) | Nessuna transizione perché è una configurazione input esclusa | ||

| 5 | Nel Flip-Flop SR l'input S=1 ed R=0 determina: | ||

| A) | La transizione dei valori output nello stato RESET | ||

| B) | La transizione dei valori output nello stato SET | ||

| C) | Il mantenimento invariato dello stato rappresentato dai valori output | ||

| D) | Nessuna transizione perché è una configurazione input esclusa | ||

| 6 | Nel Flip-Flop SR l'input S=0 ed R=1 determina: | ||

| A) | Nessuna transizione perché è una configurazione input esclusa | ||

| B) | La transizione dei valori output nello stato SET | ||

| C) | Il mantenimento invariato dello stato rappresentato dai valori output | ||

| D) | La transizione dei valori output nello stato RESET | ||

| 7 | Nel Flip-Flop SR l'input S=1 ed R=1 determina: | ||

| A) | La transizione dei valori output nello stato RESET | ||

| B) | La transizione dei valori output nello stato SET | ||

| C) | Nessuna transizione perché è una configurazione input esclusa | ||

| D) | Il mantenimento invariato dello stato rappresentato dai valori output | ||

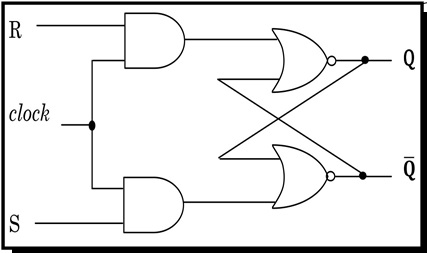

| 8 |

A partire dal Flip-Flop SR riportato in figura, il circuito del Flip/Flop D si ottiene: |

||

| A) | Eliminando la temporizzazione | ||

| B) | Ponendo S = NOT(R) | ||

| C) | Ponendo R = NOT(S) | ||

| D) | Ponento in AND gli input S ed R | ||

| 9 | Nel Flip-Flop D l'input D=1 determina: | ||

| A) | Nessuna transizione perché è una configurazione input esclusa | ||

| B) | La transizione dei valori output nello stato RESET | ||

| C) | Il mantenimento invariato dello stato rappresentato dai valori output | ||

| D) | La transizione dei valori output nello stato SET | ||

| 10 | Nel Flip-Flop D l'input D=0 determina: | ||

| A) | Il mantenimento invariato dello stato rappresentato dai valori output | ||

| B) | La transizione dei valori output nello stato SET | ||

| C) | La transizione dei valori output nello stato RESET | ||

| D) | Nessuna transizione perché è una configurazione input esclusa | ||