| TEST di autovalutazione |

| 1 |

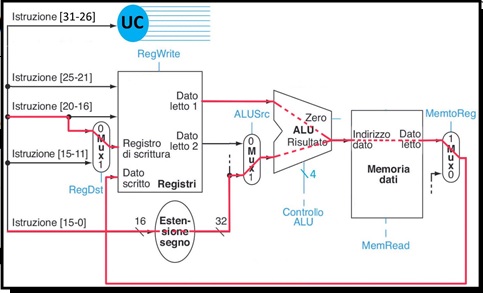

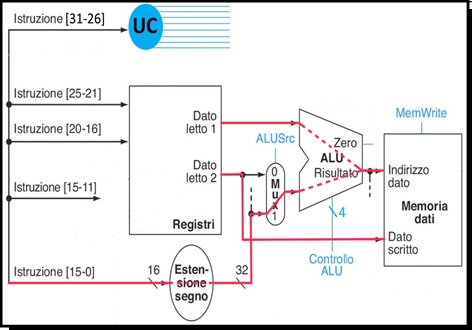

Lo schema in figura rappresenta la computazione che si svolge nella parte del circuito della CPU MIPS a ciclo singolo relativa a: |

||

| A) | Esecuzione dell'struzione di salto condizionato su uguaglianza | ||

| B) | Esecuzione dell'istruzione Load word | ||

| C) | Esecuzione delle istruzioni Aritmetico-Logiche di Tipo R | ||

| D) | Esecuzione dell'istruzione Store word | ||

| 2 |

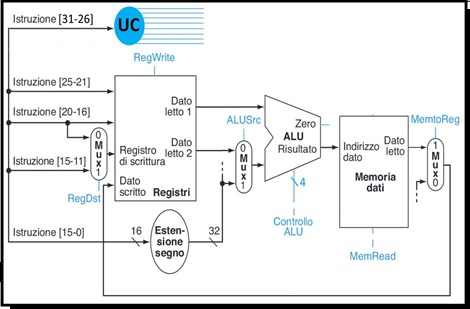

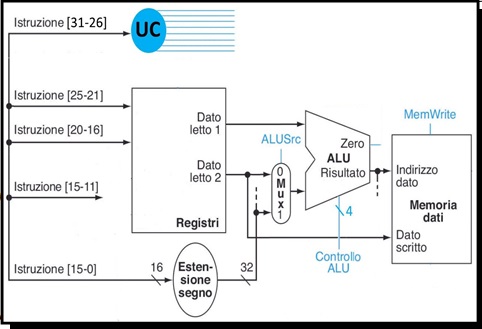

Nella parte della CPU a ciclo singolo relativa all'istruzione LOAD word riportata in figura, l'indirizzo di accesso in Memoria proviene: |

||

| A) | Direttamente dal terminale output dell'ALU che fornisce il risultato dell'addizione del contenuto nel Registro Base con indirizzo nel campo Istruzione[25-21] con il valore dell'Offset contenuto nel campo Istruzione[15-0] Esteso di segno a 32 bit | ||

| B) | Direttamente dal terminale output Dato letto 1 del blocco dei Registri, che fornisce il contenuto del registro di indirizzo Istruzione [25-21] letto anticipatamente | ||

| C) | Direttamente dal terminale output Dato letto 2 del blocco dei Registri, che fornisce il contenuto del registro di indirizzo Istruzione [20-16] letto anticipatamente | ||

| D) | Direttamente dal valore contenuto nel campo Istruzione[15-0] Esteso di segno a 32 bit | ||

| 3 |

Nella parte della CPU a ciclo singolo relativa all'istruzione LOAD word riportata in figura, il multiplexer controllato dal segnale AluSrc effettua la selezione: |

||

| A) | In base al valore AluSrc=0, che instrada in output il valore nel campo Istruzione[15-0], come operando dell'ALU | ||

| B) | In base al valore AluSrc=0, che instrada in output il valore Dato letto 2 letto anticipatamente nel blocco dei Registri, come operando dell'ALU | ||

| C) | In base al valore AluSrc=1, che instrada in output il valore nel campo Istruzione[15-0] Esteso di segno a 32 bit, come operando dell'ALU | ||

| D) | In base al valore AluSrc=1, che instrada in output il valoreDato letto1 letto anticipatamente nel blocco dei Registri, come operando dell'ALU | ||

| 4 |

Nella parte della CPU a ciclo singolo relativa all'istruzione LOAD word riportata in figura, il multiplexer controllato dal segnale MemtoReg effettua la selezione: |

||

| A) | In base al valore MemtoReg=1, che instrada in output il valore letto in Memoria attivando la lettura con MemRead=1, come dato da scrivere nel Registro del processore | ||

| B) | In base al valore MemtoReg=0, che instrada in output il risultato calcolato dall'ALU, come dato da scrivere nel Registro del processore | ||

| C) | In base al valore MemtoReg=0, che instrada in output il campo Istruzione[20-16], come indirizzo del Registro del processore dove scrivere il Dato | ||

| D) | In base al valore MemtoReg=1, che instrada in output il campo Istruzione[15-11] , come indirizzo del Registro del processore dove scrivere il Dato | ||

| 5 |

Nella parte della CPU a ciclo singolo relativa all'istruzione LOAD word riportata in figura, il multiplexer controllato dal segnale RegDst effettua la selezione: |

||

| A) | In base al valore RegDst=0, che instrada in output il risultato calcolato dall'ALU, come dato da scrivere nel Registro del processore | ||

| B) | In base al valore RegDst=1, che instrada in output il valore letto in Memoria, come dato da scrivere nel Registro del processore | ||

| C) | In base al valore RegDst=0, che instrada in output il campo Istruzione[20-16], come indirizzo del Registro del processore dove scrivere | ||

| D) | In base al valore RegDst=1, che instrada in output il campo Istruzione[15-11], come indirizzo del Registro del processore dove scrivere | ||

| 6 |

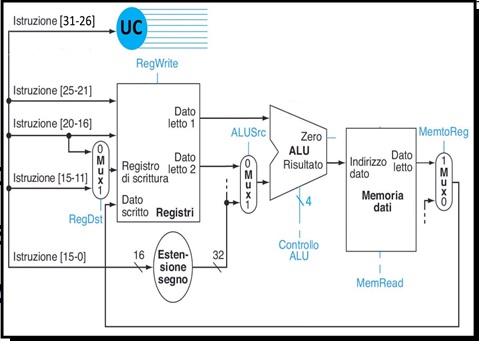

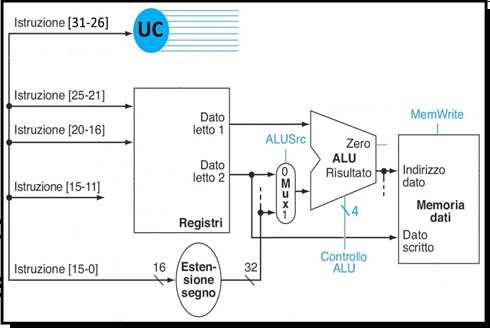

Lo schema in figura rappresenta la computazione che si svolge nella parte del circuito della CPU MIPS a ciclo singolo relativa a: |

||

| A) | Esecuzione dell'istruzione Load word | ||

| B) | Esecuzione dell'struzione Store word | ||

| C) | Esecuzione delle istruzioni Aritmetico-Logiche di Tipo R | ||

| D) | Esecuzione dell'istruzione di salto condizionato su uguaglianza | ||

| 7 |

Nella parte della CPU a ciclo singolo relativa all'istruzione STORE word riportata in figura, il multiplexer controllato dal segnale AluSrc effettua la selezione: |

||

| A) | In base al valore AluSrc=1, che instrada in output il valore nel campo Istruzione[15-0] Esteso di segno a 32 bit, come operando dell'ALU | ||

| B) | In base al valore AluSrc=0, che instrada in output il valore Dato letto 2 letto anticipatamente nel blocco dei Registri, come operando dell'ALU | ||

| C) | In base al valore AluSrc=1, che instrada in output il valoreDato letto1 letto anticipatamente nel blocco dei Registri, come operando dell'ALU | ||

| D) | In base al valore AluSrc=0, che instrada in output il valore nel campo Istruzione[15-0], come operando dell'ALU | ||

| 8 |

Nella parte della CPU a ciclo singolo relativa all'istruzione STORE word riportata in figura, l'indirizzo di accesso in Memoria proviene: |

||

| A) | Direttamente dal valore contenuto nel campo Istruzione[15-0] Esteso di segno a 32 bit | ||

| B) | Direttamente dal terminale output Dato letto 1 del blocco dei Registri, che fornisce il contenuto del registro di indirizzo Istruzione [25-21] letto anticipatamente | ||

| C) | Direttamente dal terminale output Dato letto 2 del blocco dei Registri, che fornisce il contenuto del registro di indirizzo Istruzione [20-16] letto anticipatamente | ||

| D) | Direttamente dal terminale output dell'ALU che fornisce il risultato dell'addizione del contenuto nel Registro Base con indirizzo nel campo Istruzione[25-21] con il valore dell'Offset contenuto nel campo Istruzione[15-0] Esteso di segno a 32 bit | ||

| 9 |

Nella parte della CPU a ciclo singolo relativa all'istruzione STORE word riportata in figura, il valore del Dato da scrivere in Memoria proviene: |

||

| A) | Direttamente dal terminale output dell'ALU che fornisce il risultato, e la scrittura è attivata con MemWrite=1 | ||

| B) | Direttamente dal terminale output Dato letto 2 del blocco dei Registri, che fornisce il contenuto del registro di indirizzo Istruzione [20-16] letto anticipatamente, e la scrittura è attivata con MemWrite=1 | ||

| C) | Direttamente dal Program Counter aggiornato, e la scrittura è attivata con MemWrite=1 | ||

| D) | Direttamente dal valore contenuto nel campo Istruzione[15-0] Esteso di segno a 32 bit, e la scrittura è attivata con MemWrite=1 | ||

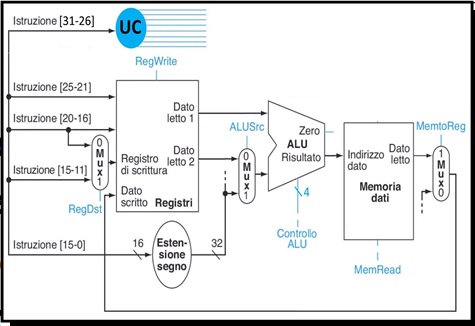

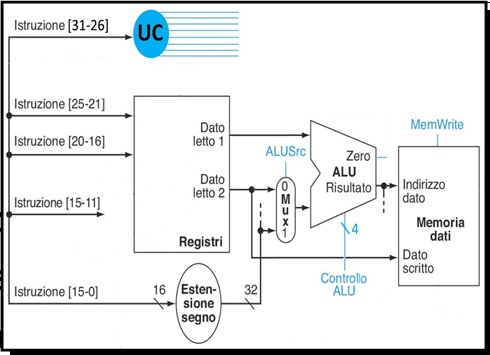

| 10 | Per le istruzioni di trasferimento dati Load word e Store word la lettura anticipata dei Registri del processore è una ottimizzazione del tempo di esecuzione perché: | ||

| A) | Fornisce sul terminale output Dato letto 1 l'indirizzo di accesso in Memoria | ||

| B) | Fornisce sul terminale output Dato letto 2 il contenuto del Registro Base di indirizzo Istruzione[15-0] come operando dell'ALU per il calcolo dell'indirizzo di accesso in Memoria | ||

| C) | Fornisce sul terminale output Dato letto 1 il contenuto del Registro da cui leggere o in cui scrivere il dato che viene trasferito | ||

| D) | Fornisce sul terminale output Dato letto 1 il contenuto del Registro Base di indirizzo Istruzione[25-21] come operando dell'ALU per il calcolo dell'indirizzo di accesso in Memoria | ||