| TEST di autovalutazione |

| 1 | La Rete Combinatoria dell'ALU a 32 bit è implementata: | ||

| A) | Mediante una Rete Sequenziale | ||

| B) | Collegando 32 ALU ad un bit relative alle specifiche posizioni con propagazione dei riporti calcolati | ||

| C) | Collegando l'ALU a 32 bit che effettua le operazioni logiche con l'ALU a 32 bit che effettua le operazioni aritmetiche. | ||

| D) | Costruendo una rete AND to OR per ciascuna operazione implementata | ||

| 2 | La propagazione del riporto nell'ALU si effettua: | ||

| A) | Inviando il segnale di controllo Operation S1S0 a tutte le ALU ad un bit relative alle singole posizioni | ||

| B) | Inviando il riporto CarryOut calcolato dall'ALU ad un bit relativa ad una posizione come dato input del multiplexer 4 a 1 dell'ALU ad un bit relativa alla posizione successiva | ||

| C) | Inviando il riporto CarryOut calcolato dall'ALU ad un bit relativa ad una posizione come segnale di controllo del multiplexer 4 a 1 dell'ALU ad un bit relativa alla posizione successiva | ||

| D) | Inviando il riporto CarryOut calcolato dall'ALU ad un bit relativa ad una posizione come riporto input CarryIn dell'ALU ad un bit relativa alla posizione successiva | ||

| 3 | Il riporto CarryIn0 input dell'ALU ad un bit relativa alla posizione meno significativa è utilizzato: | ||

| A) | Come segnale di controllo posto al valore 0 nel caso dell'Addizione, e al valore 1 nel caso della Sottrazione; negli altri casi il suo valore non influenza il risultato | ||

| B) | Per l'esecuzione delle istruzioni relative agli operatori logici AND, OR | ||

| C) | Per il controllo dell'Overflow nell'esecuzione dell'Addizione | ||

| D) | Sempre con il valore 0 | ||

| 4 |

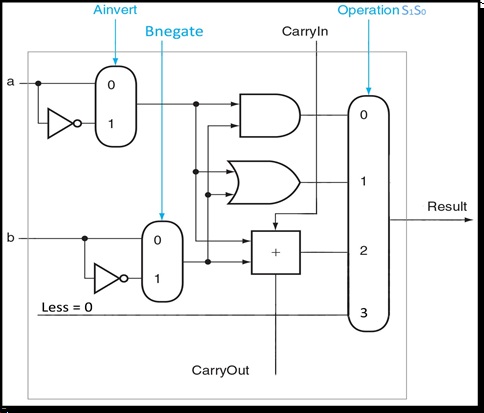

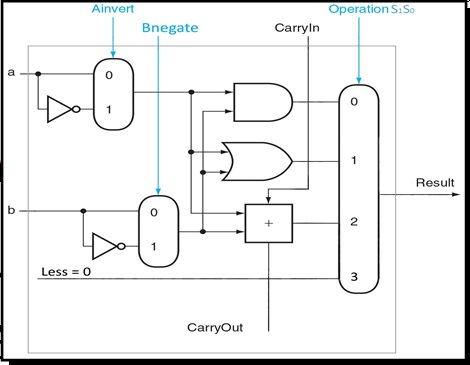

Nel circuito dell'ALU ad un bit riportato in figura, per l'esecuzione dell'istruzione SUB l'opposto del secondo operando si ottiene: |

||

| A) | Ponendo a 1 il segnale di controllo Bnegate per selezionare il valore dell'operando complementato, e ponendo a 1 il segnale di controllo CarryIn0 dell'ALU ad un bit relativa alla posizione meno significativa per sommare il valore 1 alla sequenza complementata | ||

| B) | Ponendo a 1 segnale di controllo Bnegate per selezionare il valore dell'operando complementato, e ponendo a 1 il segnale di controllo Ainvert per sommare il valore 1 alla sequenza complementata | ||

| C) | Ponendo a 1 segnale di controllo Bnegate per selezionare il valore dell'operando complementato, e ponendo a 0 il riporto input CarryIn0 dell'ALU ad un bit relativa alla posizione meno significativa | ||

| D) | Ponendo a 1 segnale di controllo Bnegate per selezionare il valore dell'operando complementato, e ponendo il segnale di controllo OperationS1S0=01 per sommare il valore 1 alla sequenza complementata | ||

| 5 |

Nel circuito dell'ALU ad un bit riportato in figura, la selezione mediante il multiplexer 4 a 1 del risultato dell'esecuzione dell'istruzione SUB si realizza: |

||

| A) | Ponendo il valore del segnale di controllo OperationS1S0=00 per scegliere l'output del Sommatore | ||

| B) | Ponendo il valore del segnale di controllo OperationS1S0=01 per scegliere l'output del Sommatore | ||

| C) | Ponendo il valore del segnale di controllo OperationS1S0=10 per scegliere l'output del Sommatore | ||

| D) | Ponendo il valore del segnale di controllo OperationS1S0=11 per scegliere l'output del Sommatore | ||

| 6 |

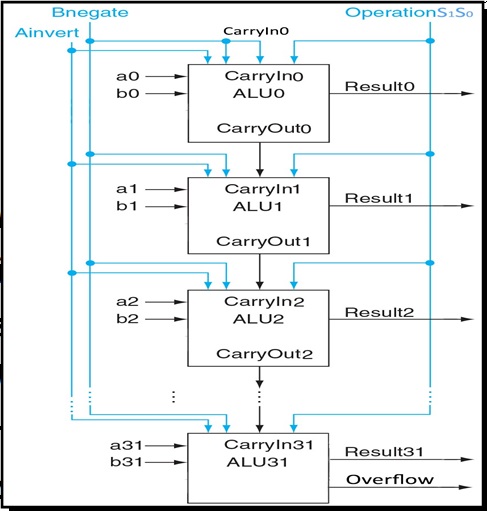

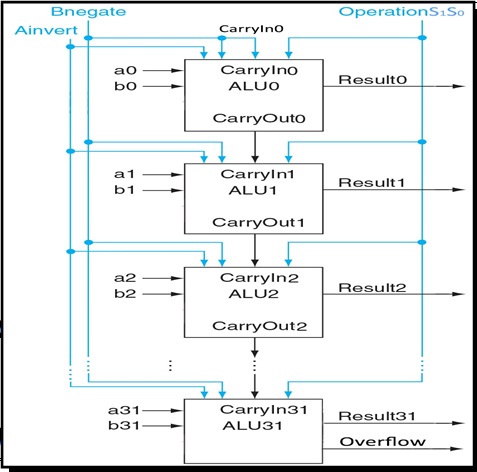

Nel circuito dell'ALU a 32 bit riportato in figura, il segnale di controllo Bnegate fornisce anche il valore del segnale di controllo CarryIn0 del riporto input dell'ALU a un bit relativa alla posizione meno significativa perché: |

||

| A) | Il valore del segnale CarryIn0 viene cambiato dal segnale Operation in base all'istruzione da eseguire | ||

| B) | Il valore del segnale Binvert viene cambiato dal segnale Operation in base all'istruzione da eseguire | ||

| C) | Il segnale CarryIn0 influenza solo le operazioni Aritmetiche che coinvolgono il Sommatore e in questi casi ha lo stesso valore del segnale Bnegate; negli altri casi il risultato non dipende dal valore di CarryIn0 | ||

| D) | I valori assunti dai due segnali sono sempre uguali per tutte le operazione eseguite dall'ALU | ||

| 7 | In base alla Legge di De Morgan l'operatore logico NOR è uguale: | ||

| A) | All'Addizione degli operandi complementati | ||

| B) | All'OR degli operandi complementati | ||

| C) | All'OR esclusivo degli operandi | ||

| D) | All'AND degli operandi complementati | ||

| 8 |

Nel circuito dell'ALU a un bit in figura, il risultato dell''istruzione NOR si ottiene: |

||

| A) | Ponendo Ainvert=1 e Bnegate=1 per complementare bit a bit gli operandi, ed il segnale di controllo OperationS1S0=00 per scegliere l'output della porta AND | ||

| B) | Ponendo Ainvert=0 e Bnegate=0 per complementare bit a bit gli operandi, ed il segnale di controllo OperationS1S0=00 per scegliere l'output della porta AND | ||

| C) | Ponendo Ainvert=1 e Bnegate=1 per complementare bit a bit gli operandi, ed il segnale di controllo OperationS1S0=10 per scegliere l'output del Sommatore | ||

| D) | Ponendo Ainvert=0 e Bnegate=0 per complementare bit a bit gli operandi, ed il segnale di controllo OperationS1S0=10 per scegliere l'output del Sommatore | ||

| 9 |

Nel circuito dell'ALU a 32 bit riportato in figura, i segnali Ainvert e Bnegate consentono di: |

||

| A) | Determinare il valore del segnale Overflow | ||

| B) | Scegliere il risultato dell'operazione effettuata dall'ALU | ||

| C) | Scegliere di effettuare la Sottrazione quando sono posti entrambi a 1 | ||

| D) | Scegliere il valore dell'operando complementato quando sono posti a 1 e non complementato quando sono posti a 0 | ||

| 10 | La pseudoistruzione dell'Assembly MIPS not $s1, $t0 è eseguita mediante: | ||

| A) | L'istruzione sub $s1, $zero, $t0 | ||

| B) | L'istruzione nor $s1, $t0, $zero | ||

| C) | L'istruzione or $s1, $t0, $zero | ||

| D) | L'istruzione and $s1, $t0, $zero | ||