| TEST di autovalutazione |

| 1 |

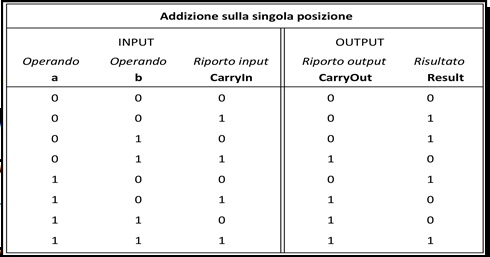

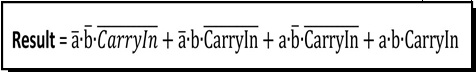

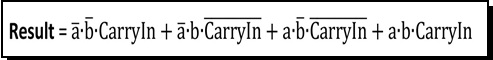

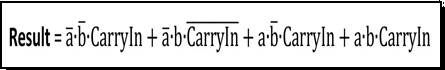

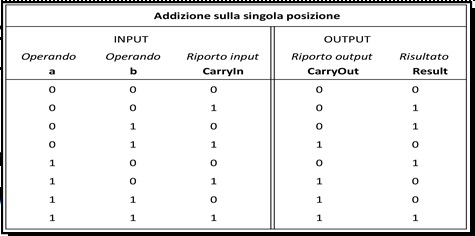

L'Espressione Booleana in forma Somma di Prodotti della funzione Resut che fornisce il bit del Risultato rappresentata nella Tavola di verità dell'Addizione riportata in figura è data da: |

||

| A) |  L'espressione in figura |

||

| B) |  L'espressione in figura |

||

| C) |  L'espressione in figura |

||

| D) |  L'espressione in figura |

||

| 2 |

L'Espressione Booleana in forma Somma di Prodotti della funzione CarryOut che fornisce il bit del Riporto sulla posizione successiva rappresentata nella Tavola di verità dell'Addizione riportata in figura è data da: |

||

| A) |  L'espressione in figura |

||

| B) |  L'espressione in figura |

||

| C) |  L'espressione in figura |

||

| D) |  L'espressione in figura |

||

| 3 |

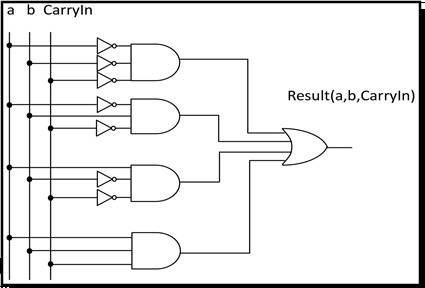

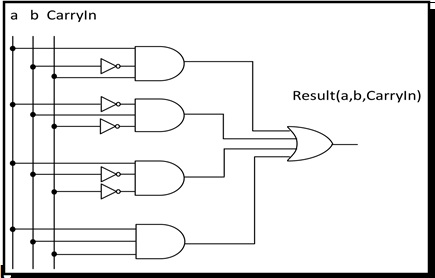

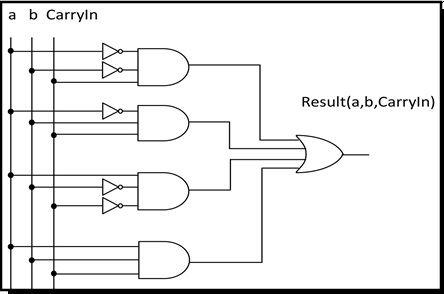

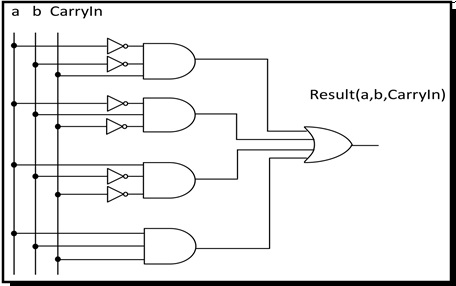

La Rete Combinatoria associata all'Espressione Booleana in forma Somma di Prodotti (rappresentata in figura) della funzione Result che fornisce il bit del Risultato dell'Addizione è data da: |

||

| A) |  Il circuito in figura |

||

| B) |  Il circuito in figura |

||

| C) |  Il circuito in figura |

||

| D) |  Il circuito in figura |

||

| 4 |

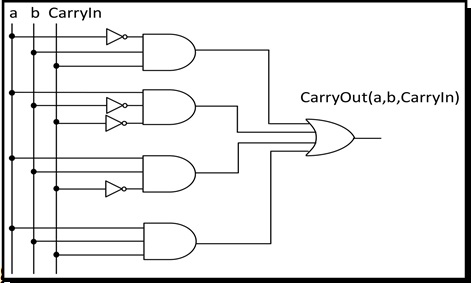

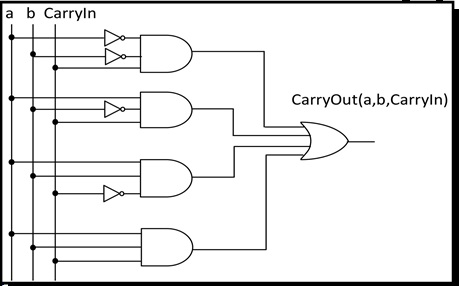

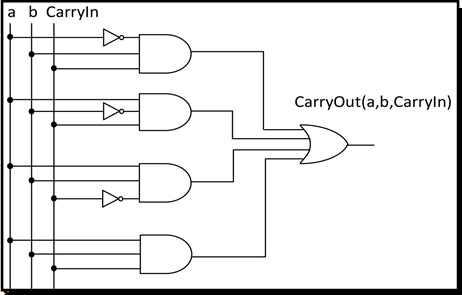

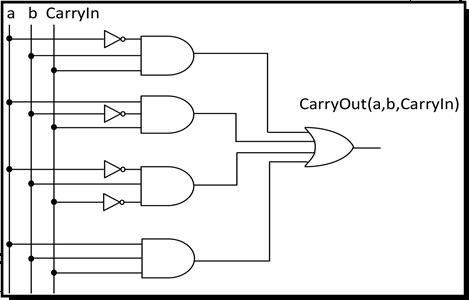

La Rete Combinatoria associata all'Espressione Booleana in forma Somma di Prodotti (rappresentata in figura) della funzione CarryOut che fornisce il bit del Riporto sulla posizione successiva è data da: |

||

| A) |  Il circuito in figura |

||

| B) |  Il circuito in figura |

||

| C) |  Il circuito in figura |

||

| D) |  Il circuito in figura |

||

| 5 |

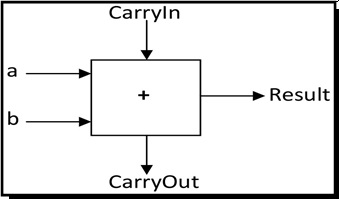

Il simbolo grafico riportato in figura rappresenta: : :

|

||

| A) | Un multiplexer 2 a 1 | ||

| B) | L'ALU a un bit relativa alla singola posizione della sequenza | ||

| C) | L'ALU a 32 bit | ||

| D) | Il Sommatore completo che calcola l'Addizione dei bit relativi alla singola posizione della sequenza binaria, costruito utilizzando le Reti Combinatorie minimali | ||

| 6 |

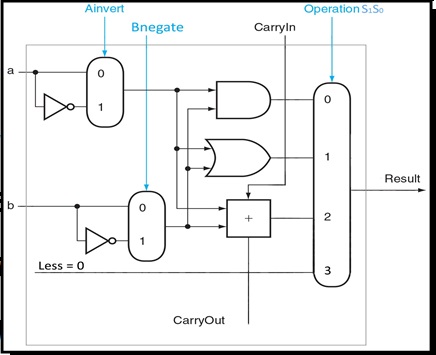

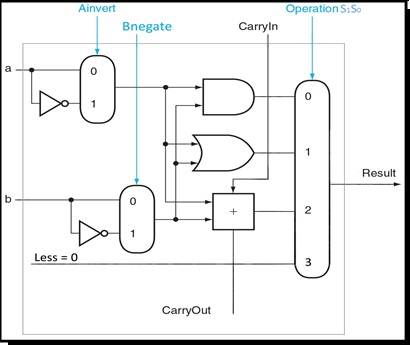

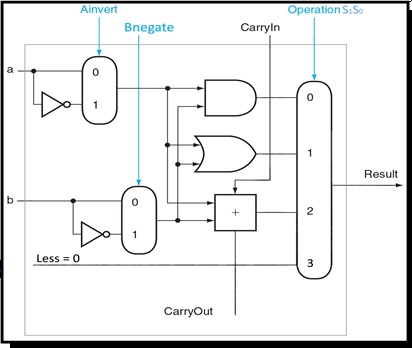

La Rete Combinatoria in figura rappresenta: |

||

| A) | L'ALU ad un bit relativa alla singola posizione della sequenza binaria | ||

| B) | Il Sommatore completo che calcola l'Addizione dei bit relativi alla singola posizione della sequenza binaria | ||

| C) | L'ALU a 32 bit | ||

| D) | Un multiplexer 2 a 1 | ||

| 7 |

Nell'ALU a un bit in figura, per selezionare il risultato delle istruzioni AND e OR ai due bit del segnale di controllo OperationS1S0 sono assegnati i valori: |

||

| A) | OperationS1S0=00 per AND, e OperationS1S0=01 per OR | ||

| B) | OperationS1S0=01 per AND, e OperationS1S0=00 per OR | ||

| C) | OperationS1S0=10 per AND, e OperationS1S0=11 per OR | ||

| D) | OperationS1S0=01 per AND, e OperationS1S0=10 per OR | ||

| 8 |

Nell'ALU a un bit in figura, per selezionare il risultato dell'istruzione ADD ai due bit del segnale di controllo OperationS1S0 sono assegnati i valori: |

||

| A) | OperationS1S0=11 | ||

| B) | OperationS1S0=00 | ||

| C) | OperationS1S0=01 | ||

| D) | OperationS1S0=10 | ||

| 9 |

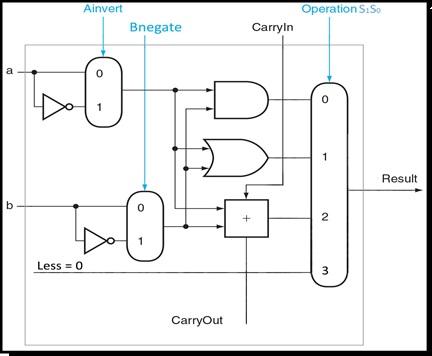

Il segnale output denotato con CarryOut nella Rete Combiatoria in figura è inviato: |

||

| A) | All'ALU ad un bit relativa alla posizione successiva come segnale di controllo del multiplexer 2 a 1 per la scelta della forma dell'operando da utilizzare | ||

| B) | All'ALU ad un bit relativa alla posizione successiva come segnale di controllo del multiplexer 4 a 1 per la scelta del risultato | ||

| C) | All'ALU ad un bit relativa alla posizione successiva come riporto input CarryIn | ||

| D) | Come output dell'ALU a 32 bit | ||

| 10 | Il segnale Less è selezionato dal multiplexed 4 a 1 nella Rete Combinatoria in figura per l'esecuzione: | ||

| A) | Dell'istruzione di salto condizionato su disuguaglianza | ||

| B) | Dell'istruzione set on less then | ||

| C) | Del calcolo dell'indirizzo di accesso in Memoria per le istruzioni load e store | ||

| D) | Per l'esecuzione della sottrazione dei due operandi | ||