| TEST di autovalutazione |

| 1 | L'esecuzione dell'istruzione Assembly MIPS slti $s1, $t2, 35: | ||

| A) | Sottrae al contenuto del registro di indirizzo $t2 il valore costante 35, e pone il risultato in $s1 | ||

| B) | Stabilisce se il contenuto del registro di indirizzo $t2 è minore del valore costante 35, e pone in $s1 il valore 1 se la relazione è vera altrimenti pone 0 | ||

| C) | Stabilisce se il contenuto del registro di indirizzo $s1 è minore del valore costante 35, e pone in $t2 il valore 1 se la relazione è vera altrimenti pone 0 | ||

| D) | Stabilisce se il contenuto del registro di indirizzo $t2 è minore del valore costante 35, e pone in $s1 il contenuto di $t2 se la relazione è vera altrimenti pone 35 | ||

| 2 | L'istruzione in Linguaggio Macchina MIPS che traduce set on less then immediato ha: | ||

| A) | Formato di Tipo I e Indirizzamento pseudodiretto | ||

| B) | Formato di Tipo I e Indirizzamento tramite Base e Offset | ||

| C) | Formato di Tipo R e Indirizzamento immediato | ||

| D) | Formato di Tipo I e Indirizzamento immediato | ||

| 3 | Il valore della costante presente nell'istruzione Assembly MIPS slti $s1, $t2, -50 viene scritto: | ||

| A) | In Notazione in modulo e segno nei 16 bit del campo immediato del formato di Tipo I | ||

| B) | In Notazione in complemento a 2 nei 16 bit del campo immediato del formato di Tipo I | ||

| C) | In Notazione posizionale pesata nei 16 bit del campo immediato del formato di Tipo I | ||

| D) | Nel registro destinazione del formato di Tipo I | ||

| 4 | L'operando costante dell'istruzione slti $s0, $t1, -70 si ottiene: | ||

| A) | Effettuando l'estensione del segno a 32 bit della sequenza di 16 bit nel campo immediato che rappresenta il valore costante | ||

| B) | Completando a 32 bit la sequenza di 16 bit nel campo immediato, che rappresenta il valore costante, aggiungendo sempre bit tutti uguali a 0 | ||

| C) | Leggendo il valore contenuto nel registro $t1 | ||

| D) | Leggendo il valore contenuto nel registro $s0 | ||

| 5 | L'operando costante dell'istruzione set on less then immediato ha un valore compreso: | ||

| A) | Tra il minimo 0 ed il massimo 232-1 | ||

| B) | Tra il minimo negativo -231 ed il massimo positivo 231-1 | ||

| C) | Tra il minimo 0 ed il massimo 216-1 | ||

| D) | Tra il minimo negativo -215 ed il massimo positivo 215-1 | ||

| 6 | L'operando costante dell'istruzione ori $s0, $t2, 25 si ottiene: | ||

| A) | Leggendo il valore contenuto nel registro $t1 | ||

| B) | Effettuando l'estensione del segno a 32 bit della sequenza di 16 bit nel campo immediato che rappresenta il valore costante | ||

| C) | Completando a 32 bit la sequenza di 16 bit nel campo immediato, che rappresenta il valore costante, con bit tutti uguali a 0 | ||

| D) | Leggendo il valore contenuto nel registro $s0 | ||

| 7 | Le istruzioni in Linguaggio Macchina MIPS che traducono le istruzioni logiche andi e ori: | ||

| A) | Hanno Formato di Tipo R e Indirizzamento immediato | ||

| B) | Hanno Formato di Tipo I e Indirizzamento tramite Base e Offset | ||

| C) | Hanno Formato di Tipo I e Indirizzamento immediato | ||

| D) | Hanno Formato di Tipo I e Indirizzamento pseudodiretto | ||

| 8 | L'istruzione Assembly MIPS ori $s0, $t3, 9 effettua: | ||

| A) | L'OR bit a bit tra il valore contenuto nel registro $s0 e il valore 9 rappresentato nei 16 bit del campo immediato completato a 32 bit aggiungendo tutti bit uguali a 0, il risultato è posto in $t3 | ||

| B) | L'OR bit a bit tra il valore contenuto nel registro $t3 e il valore 9 rappresentato nei 16 bit del campo immediato completato a 32 bit aggiungendo tutti bit uguali a 0, il risultato è posto in $s0 | ||

| C) | Il confronto tra il valore contenuto nel registro $t3 e il valore 9 rappresentato nei 16 bit del campo immediato, e pone in $s0 il valore minore | ||

| D) | Il confronto tra il valore contenuto nel registro $t3 e il valore 9 rappresentato nei 16 bit del campo immediato, e pone in $s0 il valore maggiore | ||

| 9 | Un valore la cui rappresentazione richiede più di 16 bit significativi: | ||

| A) | Può essere l'operando immediato di una istruzione Assembly MIPS con Formato di Tipo I solo se è un numero positivo | ||

| B) | Non può essere l'operando immediato di una istruzione Assembly MIPS con Formato di Tipo I | ||

| C) | Può essere l'operando immediato di una istruzione Assembly MIPS con Formato di Tipo I utilizzando la Notazione in modulo e segno | ||

| D) | Può essere l'operando immediato di una istruzione Assembly MIPS con Formato di Tipo I solo per le istruzioni con operandi unsigned | ||

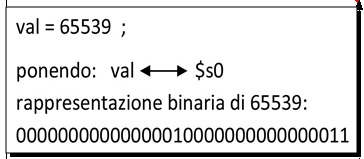

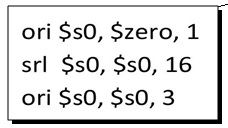

| 10 |

Le istruzioni in figura possono essere tradotte in Assembly MIPS: |

||

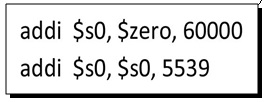

| A) |  Dalle istruzioni in figura |

||

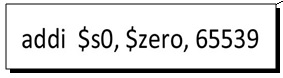

| B) |  Dall'istruzione in figura |

||

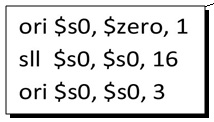

| C) |  Dalle istruzioni in figura |

||

| D) |  Dalle istruzioni in figura |

||